-

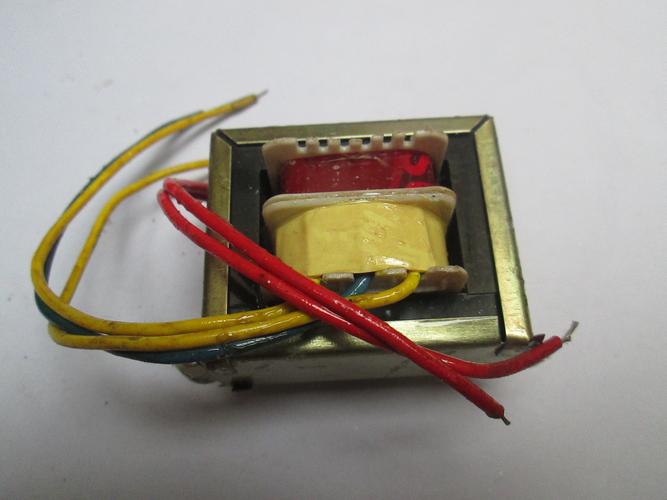

隔離變壓器安裝方式及注意事項(xiàng)隔離變壓器是一種常見的電力設(shè)備,用于將電能從一個(gè)電路傳輸?shù)搅硪粋€(gè)電路,同時(shí)實(shí)現(xiàn)電氣隔離。在安裝隔離變壓器時(shí),需要注意一些

隔離變壓器安裝方式及注意事項(xiàng)隔離變壓器是一種常見的電力設(shè)備,用于將電能從一個(gè)電路傳輸?shù)搅硪粋€(gè)電路,同時(shí)實(shí)現(xiàn)電氣隔離。在安裝隔離變壓器時(shí),需要注意一些 -

低頻變壓器使用指南:安全操作與維護(hù)要點(diǎn)低頻變壓器是一種常見的電力設(shè)備,廣泛應(yīng)用于工業(yè)生產(chǎn)和電力系統(tǒng)中。由于其特殊的工作原理和高壓電流的存在,使用低頻變壓器需要

低頻變壓器使用指南:安全操作與維護(hù)要點(diǎn)低頻變壓器是一種常見的電力設(shè)備,廣泛應(yīng)用于工業(yè)生產(chǎn)和電力系統(tǒng)中。由于其特殊的工作原理和高壓電流的存在,使用低頻變壓器需要 -

照明變壓器故障排查與解決方案照明變壓器是現(xiàn)代照明系統(tǒng)中不可或缺的重要組成部分。由于長時(shí)間使用、環(huán)境因素以及設(shè)備老化等原因,照明變壓器常常會(huì)出現(xiàn)各種故

照明變壓器故障排查與解決方案照明變壓器是現(xiàn)代照明系統(tǒng)中不可或缺的重要組成部分。由于長時(shí)間使用、環(huán)境因素以及設(shè)備老化等原因,照明變壓器常常會(huì)出現(xiàn)各種故 -

干式變壓器型號(hào)有哪些?在電力傳輸和配電系統(tǒng)中,變壓器是不可或缺的設(shè)備之一。干式變壓器作為一種常見的變壓器類型,具有許多優(yōu)點(diǎn),如可靠性高、維護(hù)簡

干式變壓器型號(hào)有哪些?在電力傳輸和配電系統(tǒng)中,變壓器是不可或缺的設(shè)備之一。干式變壓器作為一種常見的變壓器類型,具有許多優(yōu)點(diǎn),如可靠性高、維護(hù)簡

近年來,隨著各種尖端技術(shù)的不斷融合以及人們對(duì)于技術(shù)物質(zhì)需求的日益提高,便攜式電子產(chǎn)品得到了飛速發(fā)展和廣泛普及,已經(jīng)成為人們?nèi)粘I钪胁豢扇鄙俚囊徊糠帧R虼耍咝阅堋⒏咝省⒌统杀镜碾娫垂芾斫鉀Q方案已經(jīng)成為一項(xiàng)備受關(guān)注的技術(shù)關(guān)鍵和技術(shù)挑戰(zhàn)。而低壓差(LDO)線性穩(wěn)壓器以其低噪聲、高PSRR、微功耗和極低的成本,已經(jīng)成為競爭力的電源方案之一。

傳統(tǒng)的LDO線性穩(wěn)壓器在負(fù)載電流增大或輸出電容的等效串聯(lián)電阻發(fā)生變化時(shí)經(jīng)常會(huì)遇到穩(wěn)定性變差的問題。針對(duì)這個(gè)問題,本文闡述了一種準(zhǔn)確且穩(wěn)定的4.2V轉(zhuǎn)為2.5V輸出的LDO線性穩(wěn)壓器的設(shè)計(jì),該設(shè)計(jì)能夠有效解決LDO線形穩(wěn)壓器環(huán)路系統(tǒng)的穩(wěn)定問題以及其他一些諸如失調(diào)和噪聲的問題。

2系統(tǒng)框架顯示了本設(shè)計(jì)的整體系統(tǒng)框圖,采用PMOS型功率傳輸管架構(gòu)。

流置路電fe電這是因?yàn)镻MOS線性穩(wěn)壓器具有比開關(guān)穩(wěn)壓器更小的輸出噪聲和輸出紋波,比NMOS穩(wěn)壓器更低的差電壓。整個(gè)系統(tǒng)包括誤差放大器,高電流效率緩沖電路(可以改善電流效率和環(huán)路穩(wěn)定性),帶隙基準(zhǔn)源以及其修正電阻網(wǎng)絡(luò)(用于修正由于內(nèi)部電阻失調(diào)而造成的基準(zhǔn)電壓偏差),熱關(guān)斷保護(hù)電路,限流保護(hù)電路和偏置電流電路。根據(jù)運(yùn)放閉環(huán)系統(tǒng),可得到輸出為2.1頻率補(bǔ)償改進(jìn)傳統(tǒng)LDO線性穩(wěn)壓器的主要問題就是當(dāng)負(fù)載電流增加時(shí)輸出端極點(diǎn)的位置會(huì)被推向更高的頻率,而其他極點(diǎn)基本保持不變,造成系統(tǒng)穩(wěn)定性變差,并且也會(huì)限制在控制環(huán)路穩(wěn)定情況下的大負(fù)載電流。為了解決這個(gè)問題,在設(shè)計(jì)中應(yīng)用了一種改進(jìn)型密勒補(bǔ)償和高電流效率的緩沖電路。

如所示誤差放大器由NMOS晶體管Mn1 -Mp5組成,采用了共源共柵結(jié)構(gòu)以獲得更高的環(huán)路增益,從而得到良好的負(fù)載調(diào)整率、線性調(diào)整率和高電源抑制比。

本設(shè)計(jì)環(huán)路系統(tǒng)的具體電路實(shí)現(xiàn)圖而晶體管Mn6 -Mp11組成高電流效率的緩沖電路。它能夠檢測(cè)到流經(jīng)PMOS功率傳輸管的輸出電流并按照一定的比率將電流反饋到穩(wěn)壓器的轉(zhuǎn)換速率限制端。在高負(fù)載電流的情況下,輸出負(fù)載電流信號(hào)會(huì)被電路檢測(cè)而使反饋電流Ib增大。從而流過源跟隨器的電流也會(huì)被增大,這樣所增加的電流能使源跟隨器的輸出阻抗大大減小,從而使其輸出端的寄生極點(diǎn)推向更高的頻率。

另外,將補(bǔ)償電容的B端接在輸出級(jí)的輸出端,另一端A接在級(jí)中共柵放大器Mn4中的源端。從級(jí)放大的輸出端D往A點(diǎn)看就像是加入了一個(gè)源跟隨器,從而阻止了B點(diǎn)到級(jí)輸出端D點(diǎn)的前饋電流,消除了右半平面零點(diǎn)的影響并有效改善了穩(wěn)定性。

2.2帶隙基準(zhǔn)源傳統(tǒng)帶隙基準(zhǔn)源有關(guān)輸出噪聲的主要問題就是兩個(gè)PN結(jié)之間的電壓差A(yù)VEB必須要乘以一個(gè)倍乘系數(shù)M,從而實(shí)現(xiàn)溫度系數(shù)的一階補(bǔ)償。但是兩個(gè)PN結(jié)之間的電壓差A(yù)VEB的噪聲也會(huì)被乘以一個(gè)同樣的倍乘系數(shù)M,這勢(shì)必會(huì)導(dǎo)致帶隙基準(zhǔn)的輸出噪聲存在一個(gè)所不期望出現(xiàn)的增加值。在本設(shè)計(jì)中,運(yùn)用一種隨機(jī)噪聲的基本概念來實(shí)現(xiàn)比傳統(tǒng)帶隙基準(zhǔn)更低的輸出噪聲。這個(gè)概念的原理就是用幾個(gè)AVEB電壓的求和來替代將AVEB電壓乘以一個(gè)倍乘系數(shù)0.利用這種方法,輸出噪聲的結(jié)果可以表示為發(fā)射極-基極電壓的內(nèi)部噪聲;Vn??AVEB電壓的內(nèi)部噪聲;M補(bǔ)償溫度系數(shù)所需要的增益因數(shù)。

顯示了本設(shè)計(jì)中低噪聲拓?fù)浣Y(jié)構(gòu)的帶隙基準(zhǔn)源的具體電路。它包括了啟動(dòng)電路、偏置電流電路、AVEB電壓產(chǎn)生電路以及一個(gè)低通濾波器。為了改進(jìn)電路中CMOS放大器的性能,我們利用斬波穩(wěn)定放大器63來減小放大器的1/f噪聲和失調(diào)電壓,終可得到的基準(zhǔn)電壓為1.2V. 2.3熱關(guān)斷保護(hù)電路如所示,雙極型晶體管的發(fā)射極基極電壓與VT產(chǎn)生器的輸出電壓分別具有負(fù)和正的溫度系數(shù)。由于兩個(gè)比較器的輸入電壓Vd,Vd都與溫度成正比,兩個(gè)比較器的輸出電壓則允許通過適當(dāng)?shù)卦O(shè)置溫度T=T.時(shí)的電壓值Vd(T)和匕⑴以及Mi與化的值,分別從溫度到 熱關(guān)斷保護(hù)電路的功能框。4限流保護(hù)電路如所示,電流檢測(cè)電路可以瞬時(shí)地檢測(cè)流經(jīng)功率傳輸管的輸出電流并且以一定的比率系數(shù)1/K將輸出電流信號(hào)反饋回來。隨著輸出電流的增大,反饋電流Ifb也會(huì)隨之增大。一旦輸出電流接近大負(fù)載電流時(shí),比較器正端的電壓便會(huì)大于Vrf而使比較器輸出為高,從而使NMOS管Mn1導(dǎo)通。接著PMOS管Mn2也會(huì)因?yàn)槠玫膶?dǎo)通而開啟,于是功率傳輸管的柵端電壓被Mn2管拉到高,繼而被關(guān)斷。 3版圖與后仿結(jié)果平臺(tái)下米用TSMC-0.35m-2P3M的CMOS混合信號(hào)工藝進(jìn)行版圖設(shè)計(jì)和后仿真。版圖如所示,版圖在通過DRC和LVS驗(yàn)證后在芯片輸入電源電壓為4. 2V,外接的輸出電容為2.2F,其等效串聯(lián)電阻ESR值為0.0m的條件下對(duì)系統(tǒng)進(jìn)行后仿真。仿真波形如。 系統(tǒng)版圖可見,整個(gè)電壓穩(wěn)壓器可以驅(qū)動(dòng)的輸出負(fù)載電流大于300mA,且當(dāng)負(fù)載電流由0突變到300mA時(shí),穩(wěn)壓器輸出電壓的大變化小于60mV.電源電壓抑制比在10kHz時(shí)仍能達(dá)到60dB以上。 4結(jié)束語通過后仿真結(jié)果可看出整個(gè)系統(tǒng)的穩(wěn)定性幾乎不隨著負(fù)載電流的增加而減少,對(duì)于低ESR的輸出電容也能保持穩(wěn)定,在負(fù)載與輸入電壓突然變化時(shí)依然能夠保持穩(wěn)定輸出而不會(huì)發(fā)生振蕩,達(dá)到了本設(shè)計(jì)目的。但仍然有許多不足之處有待完善,例如:如何使穩(wěn)壓器在更小的輸出電容下保持穩(wěn)定輸出;如何在保持大功率的輸出能力的時(shí)又能有效縮減芯片尺寸大小等問題。